| Realtime Signal Analyser with Cyclone 4 | |||

|

Cyclone IV 48kHz / 96kHz user rate 200 MHz sample rate |

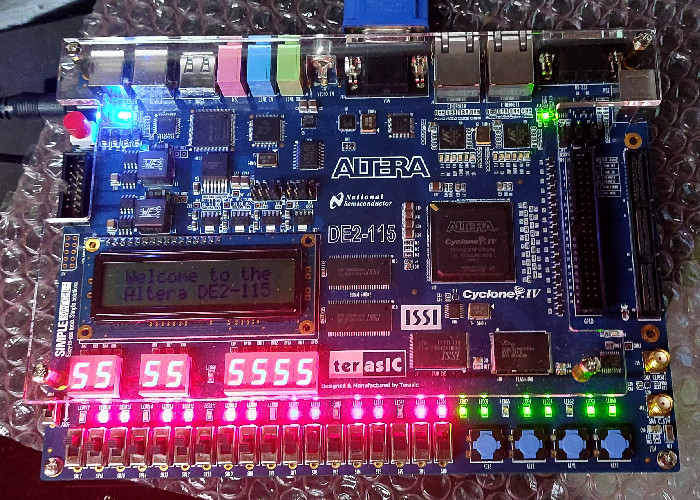

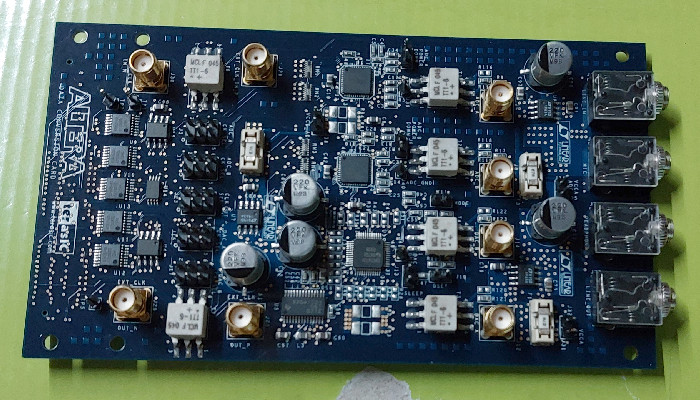

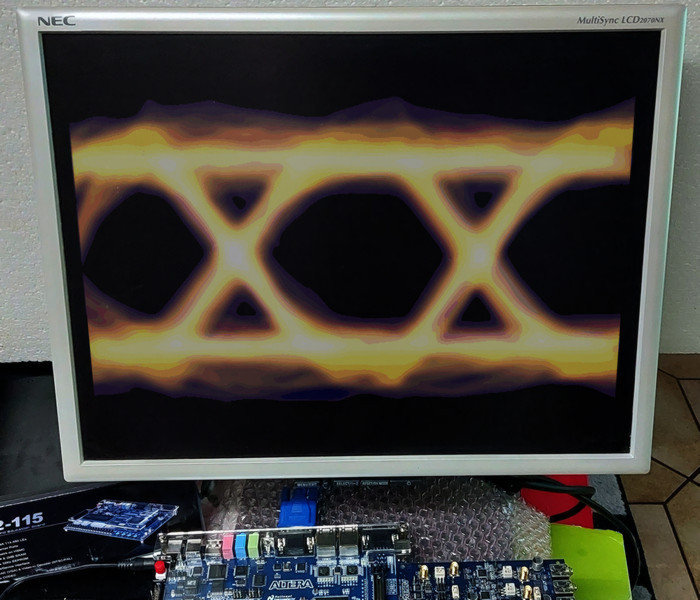

Base Hardware Unit Altera Cyclone IV + ADC/DAC board  Altera base board with Cyclone 4 The Altera Cyclone 4 DE2-115 from Terasic is used to implement a high resolution signal generator and alayser for technical signal tests to be used for connections in between PCBs. The test data is stored in the block RAMs and then continously driven out with any given frequency. A 150Msps - DAC is used here to shape signals typically used for audio data transmission like TDM and S/PDIF. In the example shaping is performed with 8 dots per clock, leading to almost 100MHz to define the analog behaviour of the 12,288MHz BMC clock for 96kHz Audio in terms of rising and overshot.  Terasic DAC-ADC-board for Cyclone 4 The incoming signal is sampled with twice the driver clock using 4 different phases of the PLL with settings 0°, 90°, 180°, 270° to statically oversample the signal. This leads to 64 positions for each sample of the S/PDIF clock. Together with the programable output delays of the driving Pin in the FPGA, 640 positions are possible altogether. An area of 640x400 dots is used to store the accumulated number of crossings of the signal for this combination of voltage and time leading to then known eye pattern diagram. The received and reconstructed S/PDIF signal is monitored at the line out ports of the Terassic DAC board for test purposes.  Eye Pattern of a 192kHz S/PDIF signal Click here for details of the signal generation with the multi rate clock resampler and the pulse shaper. Get the VHDL code here: sa_2012_os.zip Click here to see the Sampler |

||

|

|

|||

© Dipl.-Ing. Jürgen Schuhmacher 2012