| Wavetable Module for the Music Synthesizer in VHDL | |||

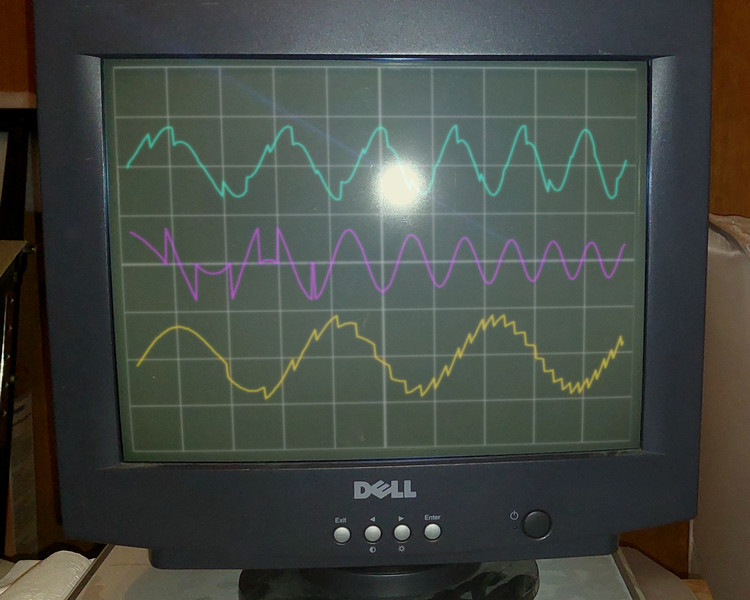

| WAVE TABLE Module 1024 Samples RAM 48kHz x 16 Bit | VHDL Block Design Signal flow in the PLD  An optimized DDS module is used to equip the workstation with a precise wave table based sound generation. Using either DDS-based frequency generation or VA-modeled sine wave operation, a trigger sine wave is used to control the current phase of the sound signal. According to the given frequency setting a multiple of it is used to generate the address for the SRAM in the FPGA leading to a precise phase relation of both the triggering wave and the generated wave thus eg 256, 512 or even 1024 dots per period can be accessed progressively. Any waveform or sets of waveforms can be loaded into the blockram so true wave table synthesis is performed when walking through them. Phase jitter is eliminated by oversampling the wave with the FPGA clock frequency. For a 12 kHz wave, 4096 samples are used to generate the 4 samples for the 48kHz output using a CIC + FIR filter. Blockram is accessed by a simple UART. Real time S/PDIF sampling is planned. Example Output Signals from the PLD  Example Waves on VGA Oscilloscope view See also Reverb Module. | ||

| 96 kHz Audio DSP | |||

| |||

© Sound of L.A. Music Productions 2006