| Analog Input Module for the Music Synthesizer | |||

|

PLD ADC Module 10kHz x 12 Bit |

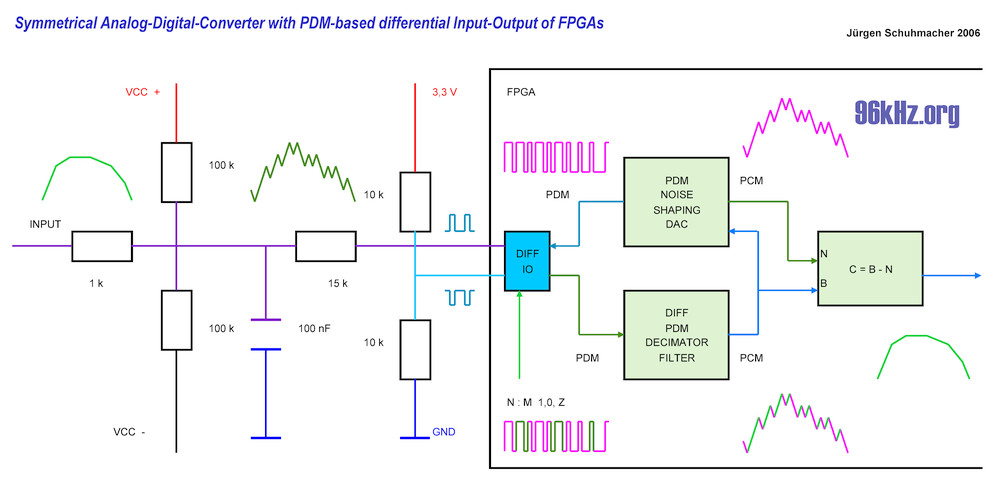

FPGA-Platform Xilnx Spartan 3E 500 An Spartan 3E platform is used to implement a test design for a versatile VHDL-module to turn common FPGA-IOs into flexible programable ADC-Converters to read out potentiometers and also analog voltages with alternating current (AC).  The circuit is an extended verion of the simple version presented here PLD-PDM-ADC which is capable of reading voltages from 0 ... 3V. As described this is done by adding a regulated noise to the input signal making it possible to read it with a comparator built in the FPGA IO. By using a tricky PDM and a R-R-circuit for potential shift at the front, it is also possible to read negative voltages with this version. Circuit Function Several parametric functions are used to apply edge shaping of a formery linear signal. Because of the limited number of Multipliers in the Spartan 3E of only 20, a full parallel implementation is limited to 8 functions altogether and a x16 in maximum because of the required number of square operations. With forthcoming FPGAs more waves shall be possible.  IO-extension for FPGA-Pins to drive and read out the voltage of a capacitor allowing ADC-function Unlike a typical PDM-based ADC there is two special functions used: A controlled regulation loop is applied which optimizes the PDM-output of the modulation pin using noise shaping strategy. Secondly a switchable buffer of the IO is used to drive the pin either with the 0-1-PDM or also with an open signal ("Z") in order to read the state of the comparator to obtain a new PDM signal. Depending on the mode (driven or undriven) it is possible to switch in between precision and bandwidth, since the input signal in the first case contains a large amount (and at all) the ouput signal during some periods but allows a higher accuracy when balancing the capacitor. In both cases the input signal is masked and decimated. Finally a suitable amount of the introduced noise is substracted from the derived PCM signal to obtain a most clean analog input signal. Signal Processing The input and outputs are switched according to the demanded frequency setting and cover a large spectrum of possible frequencies. With an addition option to set the input to a propper analog GND, it is also possible to automatically calibate the input. For FPGAs and PLDs this is essential since the switch point of the Schmitt-input is often far away from 50%. For manual calibration the two REF-Rs might be replaced by a Potentiometer to tune the negative input of the comparator. For the Spartan 3E device I found PDM relations of up 60% - 40% for a 50% input signal / a GND in symmetry use respectivly. For high precision demands, without making calibration necessary an external OpAmp should be used to do this in a better way. Using a well calibrated circuit with 3 REF-points and a balancing signal processing it is possible to process DC-signals with up to 14-15 bit precision and finally achieve an ADC suitable for up to up to 50 kHz when using a modern 100 MHz FPGA. The Spartan board here runs at almost 50 MHz (compatible to 96k S/PDIF) and picks up 10kHz sine waves with around 12 bit precision. A classical pink noise like audio signal is typically fetched in a way that is is possible to perform a FFT or show it on my internal FPGA-oscilloscope. Read about the former circuit PLD-PDM-ADC. Read about the application Audio-to-MIDI-Converter |

||

|

96 kHz Audio DSP |

|||

|

|

|||

© Sound of L.A. Music Productions 2006